На отчетном мероприятии в конце этой недели выступил генеральный директор TSMC Си-Си Вэй. Он заявил, что N3E расширяет семейство технологии N3 и предлагает улучшенные характеристики, такие как повышенная производительность, уменьшенное энергопотребление и высокий уровень годной продукции. Он также отметил, что данная технология обеспечивает полную поддержку платформ как в сегменте высокопроизводительных вычислений, так и для применения в смартфонах. По его словам, N3E успешно прошел квалификационные тесты, достигнув запланированных показателей производительности и качества, и его массовое производство будет запущено в четвёртом квартале текущего года.

На этой неделе руководство TSMC выразило оптимистичные ожидания относительно долгосрочного спроса на семейство 3-нм техпроцессов, предоставляемых компанией. В TSMC надеются, что эти технологии будут иметь продолжительный жизненный цикл на рынке и будут востребованы клиентами долгое время. По прогнозам, к концу текущего года базовый техпроцесс N3 будет приносить от 4 до 6% общего дохода компании. Он уже используется в серийном производстве с начала текущего года, но в отчетности компании не фигурирует.

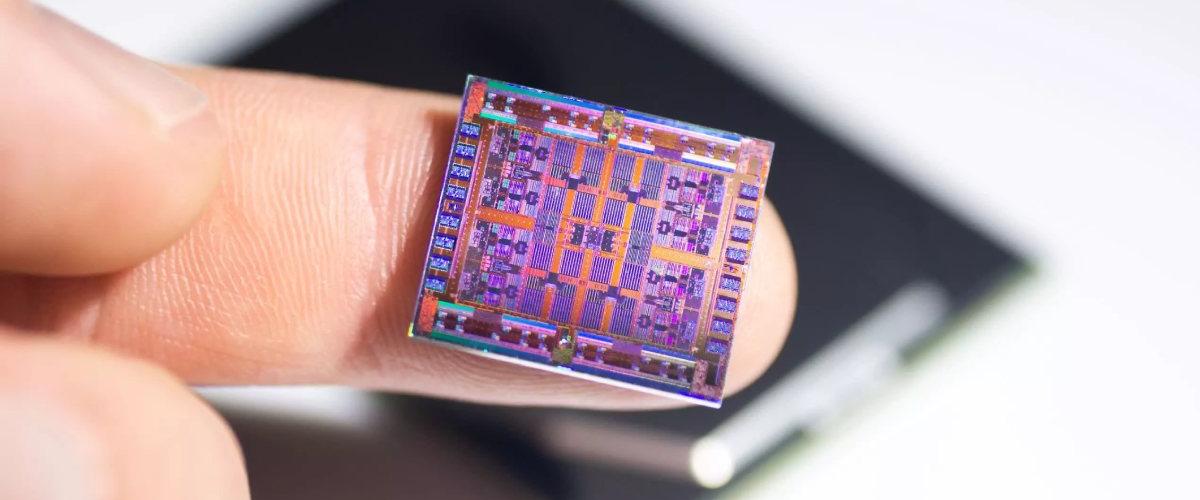

Базовый вариант техпроцесса N3, который компания TSMC использует для массового производства компонентов, по заказу той же Apple с конца прошлого года, обеспечивает снижение энергопотребления до 25–30%, улучшение производительности на 10–15% и экономию площади кристалла до 42% по сравнению с техпроцессом N5. Что касается N3E, то за счет некоторого уменьшения плотности размещения транзисторов (на 7,8% по сравнению с N3), этот техпроцесс предлагает более высокий уровень выхода годной продукции, упрощение самого производства, и как следствие — снижение себестоимости продукции.

Кроме того, N3E увеличивает экономию в энергопотреблении до 32% по сравнению с N5, а производительность транзисторов возрастает до 18% с 15% у базового N3.

N3E лишь незначительно жертвует плотностью размещения транзисторов по сравнению с N5, увеличивая ее на 1,6 раза вместо 1,7 раз у более дорогостоящего N3. Ожидается, что N3E сможет привлечь больше клиентов к услугам TSMC по сравнению с N3.

TSMC не ограничивается только двумя разновидностями 3-нм техпроцесса. К концу второй половины следующего года компания планирует освоить техпроцесс N3P, который обещает снижение энергопотребления на 5–10% по сравнению с N3E, повышение быстродействия на 5% и увеличение плотности размещения транзисторов на 4%.

В перспективе, к 2025 году, для производства самых производительных чипов TSMC внедрит техпроцесс N3X. Этот техпроцесс позволит применять более высокое напряжение и повысит производительность как минимум на 5%, но ценою более высокого энергопотребления по сравнению с N3P. Плотность размещения транзисторов останется на одном уровне с N3P.