Современные модели ИИ должны переносить колоссальные объемы данных между памятью, хранящей информацию, и вычислительными блоками, которые ее обрабатывают. На обычных 2D-чипах компоненты располагаются на одной плоскости с ограниченным, распределенным объемом памяти, поэтому перенос данных происходит по длинным, перегруженным маршрутам. Поскольку вычислительные элементы работают намного быстрее, чем осуществляется передача данных, и поскольку чип не может хранить достаточно памяти поблизости, система постоянно ожидает информации. Инженеры называют эту проблему «стеной памяти» — состоянием, в котором скорость обработки превышает способность чипа передавать данные.

В течение десятилетий производители чипов решали проблему «стены памяти», уменьшая транзисторы и увеличивая их количество на чипе. Но потенциал этого подхода не безграничен.

Новый чип решает проблему «стены памяти», вырастая вверх, пишет Stanford News.

«Благодаря вертикальной интеграции памяти и вычислительных систем мы можем передавать гораздо больше информации гораздо быстрее, подобно тому, как лифтовые шахты в высотном здании позволяют перемещаться между этажами одновременно множеству жителей», — сказал Татагата Шримани из Университета Карнеги-Меллона, один из авторов статьи.

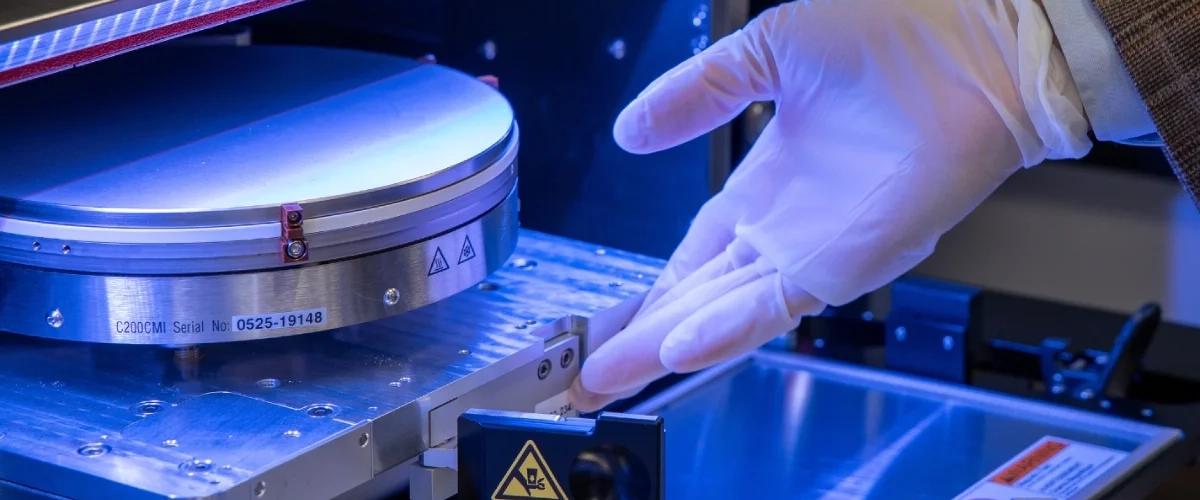

Вместо послойного изготовления 3D-чипа команда создавала каждый слой непосредственно поверх предыдущего, в едином непрерывном процессе. Такой метод позволяет укладывать компоненты и соединять их гораздо плотнее.

«Это открытие — путь к новой эре производства микросхем и инновациям, — сказал Субхасиш Митра из Стэнфордского университета, ведущий исследователь. — Именно такие прорывы позволят нам достичь тысячекратного повышения производительности оборудования, которое потребуется будущим системам искусственного интеллекта».

Первые аппаратные тесты показали, что прототип уже превосходит сопоставимые 2D-чипы примерно в четыре раза. Моделирование будущих версий — с большим количеством слоев памяти и вычислительных ресурсов — дает основание рассчитывать на еще больший прирост производительности: до двенадцати раз в реальных задачах ИИ.

По словам исследователей, такая архитектура открывает путь к 100-1000-кратному улучшению произведения мощности на задержку, ключевого показателя, который уравновешивает скорость и энергоэффективность. За счет резкого сокращения передачи данных и добавления множества вертикальных путей чип может достичь как более высокой пропускной способности, так и более низкого энергопотребления на операцию — сочетание, которое долгое время считалось для традиционных двухмерных архитектур недостижимым.

В начале года инженеры из США разработали новый технологический процесс интеграции высокопроизводительных транзисторов GaN в стандартные кремниевые КМОП-чипы — недорогой, масштабируемый, а также совместимый с существующим оборудованием для производства полупроводников.