Хотя Samsung начнет эксплуатацию своей High-NA EUV-системы на год позже Intel, компания все же опередит конкурентов, таких как TSMC и SK hynix. Когда High-NA EUV начнет применяться в массовом производстве, пока неизвестно, но это, вероятно, произойдет во второй половине текущего десятилетия.

Samsung активно развивает экосистему вокруг технологии High-NA EUV. В сотрудничестве с японской компанией Lasertec компания занимается разработкой оборудования для проверки фотомасок, специально предназначенных для High-NA EUV. Samsung уже приобрела инспекционный инструмент Lasertec Actis A300, который значительно улучшает контрастность изображений.

Также Samsung взаимодействует с JSR, производителем фоторезистов, и Tokyo Electron, компанией, создающей оборудование для травления, с целью подготовки к коммерческому внедрению High-NA EUV к 2027 году. Компания сотрудничает с Synopsys, чтобы перейти от традиционных схем на фотомасках к криволинейным, что позволит точнее создавать схемы на пластинах.

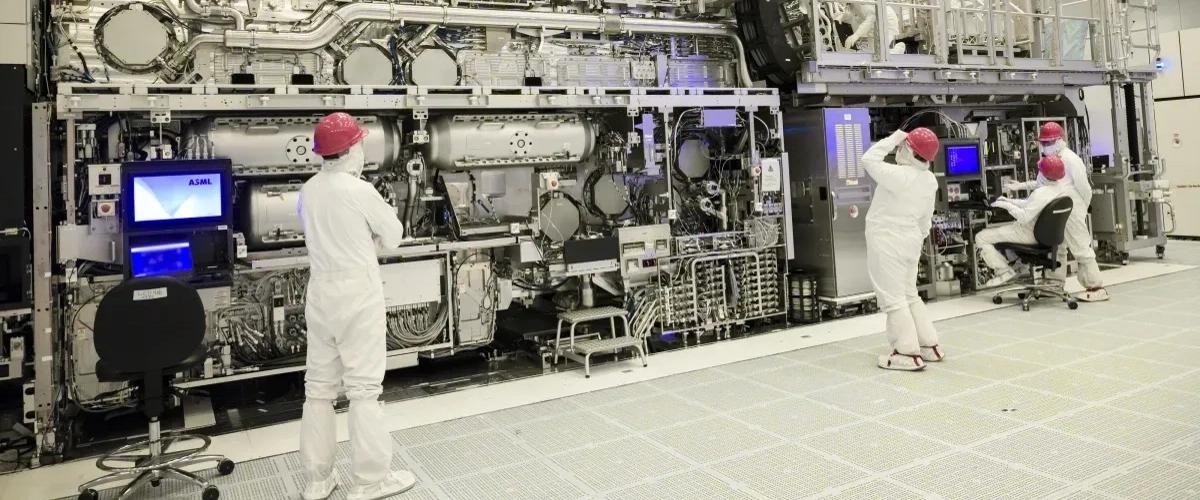

High-NA EUV-системы, разработанные ASML, способны достигать разрешения в восемь нанометров, что существенно улучшает показатели по сравнению с текущими Low-NA EUV-системами, которые ограничены 13 нанометрами при одном экспонировании. Это позволит уменьшить размеры транзисторов примерно в 1,7 раза и увеличить их плотность почти в три раза. Переход на High-NA EUV также устранит необходимость в двойном паттернинге, что может упростить производство и потенциально снизит затраты.

Однако переход на High-NA сопровождается рядом проблем. Эти системы стоят дороже (от $380 до $400 миллионов) и требуют значительных изменений в проектировании чипов из-за уменьшенного вдвое поля изображения. Кроме того, их больший размер потребует изменения планировок фабрик, чтобы разместить новое оборудование.